# 16-Channel Short Haul T1/E1/J1 Line Interface Unit IDT82P20416

Version - December 17, 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: 1-800-345-7015 or 408-284-8200• TWX: 910-338-2070 • FAX: 408-284-2775

Printed in U.S.A.

© 2009 Integrated Device Technology, Inc.

| DISCLAIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LIFE SUPPORT POLICY Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is exe-                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| cuted between the manufacturer and an officer of IDT.  1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in                                                                                                                                                                                                                                                                                                                                                                                                         |

| accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  2. A critical component is any components of a life support device or system, or to affect its                                                                                                                                                                                                                                                                                                                                                                                                                              |

| safety or effectiveness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **Table of Contents**

| T/ | BLE  | OF CC          | NTENTS                                                                    | 3  |

|----|------|----------------|---------------------------------------------------------------------------|----|

| LI | ST O | F TABL         | ES                                                                        | 6  |

|    |      |                | RES                                                                       |    |

|    |      |                |                                                                           |    |

|    |      |                | IS                                                                        |    |

|    |      |                |                                                                           |    |

|    |      |                |                                                                           |    |

|    |      |                | RAM                                                                       |    |

|    |      |                | NMENT                                                                     |    |

|    |      |                | RIPTION                                                                   |    |

| 3  |      |                | AL DESCRIPTION                                                            |    |

|    | 3.1  | T1 / E         | 1 / J1 MODE SELECTION                                                     | 20 |

|    | 3.2  | RECE           | VE PATH                                                                   |    |

|    |      | 3.2.1          | Rx Termination                                                            |    |

|    |      |                | 3.2.1.1 Receive Differential Mode                                         |    |

|    |      | 3.2.2          | Equalizer                                                                 |    |

|    |      |                | 3.2.2.1 Line Monitor                                                      |    |

|    |      | 000            | 3.2.2.2 Receive Sensitivity                                               |    |

|    |      | 3.2.3          | Slicer                                                                    |    |

|    |      | 3.2.4<br>3.2.5 | Rx Clock & Data Recovery  Decoder                                         |    |

|    |      | 3.2.5          | Receive System Interface                                                  |    |

|    |      | 3.2.7          | Receiver Power Down                                                       |    |

|    | 33   | -              | SMIT PATH                                                                 |    |

|    | 0.0  | 3.3.1          | Transmit System Interface                                                 |    |

|    |      | 3.3.2          | Tx Clock Recovery                                                         |    |

|    |      | 3.3.3          | Encoder                                                                   |    |

|    |      | 3.3.4          | Waveform Shaper                                                           | 25 |

|    |      |                | 3.3.4.1 Preset Waveform Template                                          |    |

|    |      |                | 3.3.4.2 User-Programmable Arbitrary Waveform                              |    |

|    |      | 3.3.5          | Line Driver                                                               |    |

|    |      | 000            | 3.3.5.1 Transmit Over Current Protection                                  |    |

|    |      | 3.3.6          | Tx Termination                                                            |    |

|    |      | 227            | 3.3.6.1 Transmit Differential Mode                                        |    |

|    |      | 3.3.7<br>3.3.8 | Transmitter Power DownOutput High-Z on TTIP and TRING                     |    |

|    | 3 /  |                | R ATTENUATOR (RJA & TJA)                                                  |    |

|    |      |                | IOSTIC FACILITIES                                                         |    |

|    | 0.0  | _              | Ripolar Violation (RPV) / Code Violation (CV) Detection and RPV Insertion | 11 |

|   |            |         | 3.5.1.1 Bipolar Violation (BPV) / Code Violation (CV) Detection | 33 |

|---|------------|---------|-----------------------------------------------------------------|----|

|   |            |         | 3.5.1.2 Bipolar Violation (BPV) Insertion                       | 33 |

|   |            | 3.5.2   | Excessive Zeroes (EXZ) Detection                                |    |

|   |            | 3.5.3   | Loss of Signal (LOS) Detection                                  |    |

|   |            |         | 3.5.3.1 Line LOS (LLOS)                                         | 34 |

|   |            |         | 3.5.3.2 System LOS (SLOS)                                       |    |

|   |            |         | 3.5.3.3 Transmit LOS (TLOS)                                     |    |

|   |            | 3.5.4   | Alarm Indication Signal (AIS) Detection and Generation          |    |

|   |            |         | 3.5.4.1 Alarm Indication Signal (AIS) Detection                 |    |

|   |            |         | 3.5.4.2 (Alarm Indication Signal) AIS Generation                |    |

|   |            | 3.5.5   | PRBS, QRSS, ARB and IB Pattern Generation and Detection         |    |

|   |            |         | 3.5.5.1 Pattern Generation                                      |    |

|   |            |         | 3.5.5.2 Pattern Detection                                       |    |

|   |            | 3.5.6   | Error Counter                                                   |    |

|   |            |         | 3.5.6.1 Automatic Error Counter Updating                        |    |

|   |            |         | 3.5.6.2 Manual Error Counter Updating                           |    |

|   |            | 3.5.7   | Loopback                                                        |    |

|   |            |         | 3.5.7.1 Analog Loopback                                         |    |

|   |            |         | 3.5.7.2 Remote Loopback                                         |    |

|   |            | 0 = 0   | 3.5.7.3 Digital Loopback                                        |    |

|   |            | 3.5.8   | Channel 0 Monitoring                                            |    |

|   |            |         | 3.5.8.1 G.772 Monitoring                                        |    |

|   |            | 01 0 01 | 3.5.8.2 Jitter Measurement (JM)                                 |    |

|   | 3.6        |         | K INPUTS AND OUTPUTS                                            |    |

|   |            | 3.6.1   | Free Running Clock Outputs on CLKT1/CLKE1                       |    |

|   |            | 3.6.2   | MCLK, Master Clock Input                                        |    |

|   | ٥ -        | 3.6.3   | XCLK, Internal Reference Clock Input                            |    |

|   |            |         | RUPT SUMMARY                                                    |    |

| 4 | MIS        | CELLAN  | NEOUS                                                           | 51 |

|   | 4.1        | RESET   | Γ                                                               | 51 |

|   |            | 4.1.1   | Power-On Reset                                                  | 52 |

|   |            | 4.1.2   | Hardware Reset                                                  | 52 |

|   |            | 4.1.3   | Global Software Reset                                           | 52 |

|   |            | 4.1.4   | Per-Channel Software Reset                                      | 52 |

|   | 4.2        | MICRO   | DPROCESSOR INTERFACE                                            | 52 |

|   | 4.3        | POWE    | R UP                                                            | 53 |

|   | 4.4        | HITLES  | SS PROTECTION SWITCHING (HPS) SUMMARY                           | 53 |

| 5 |            |         | MING INFORMATION                                                |    |

| - |            |         | STER MAP                                                        |    |

|   | J. I       | 5.1.1   |                                                                 |    |

|   |            | 5.1.1   | Per-Channel Register                                            |    |

|   | <b>5</b> 2 | -       | · · · · · · · · · · · · · · · · · · ·                           |    |

|   | J.Z        |         | STER DESCRIPTION                                                |    |

|   |            | 5.2.1   | Global Register Per-Channel Register                            |    |

|   |            | J.Z.Z   | F CI-VII ALII ICI NEUISIEI                                      | 00 |

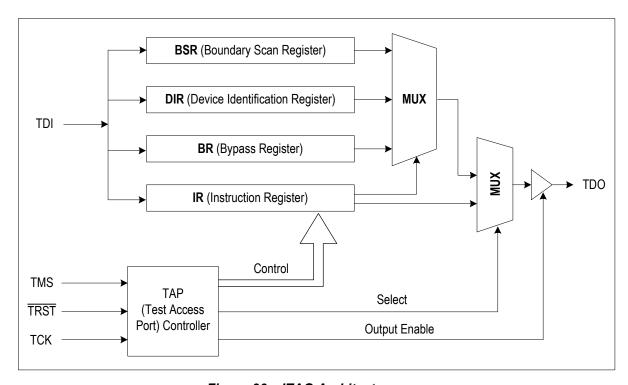

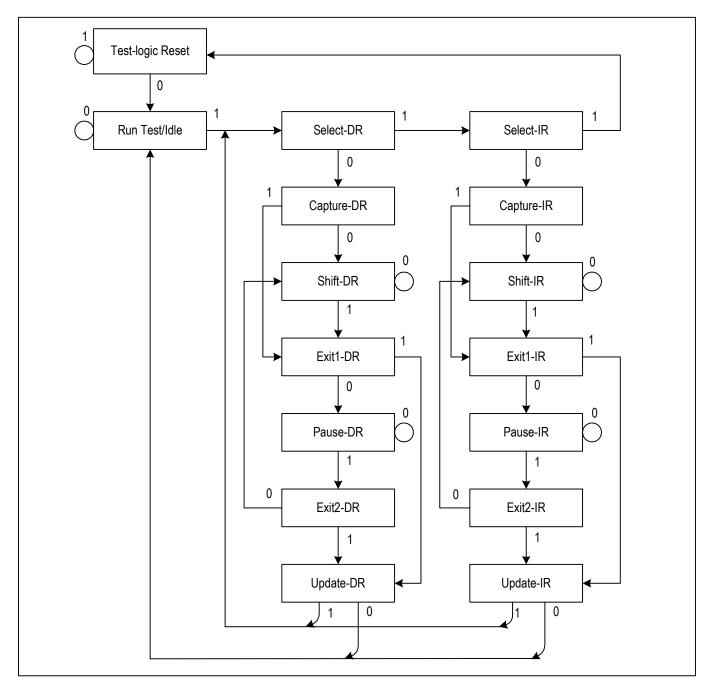

| 6  | JTAG                                                     | 95  |

|----|----------------------------------------------------------|-----|

|    | 6.1 JTAG INSTRUCTION REGISTER (IR)                       | 95  |

|    | 6.2 JTAG DATA REGISTER                                   | 95  |

|    | 6.2.1 Device Identification Register (IDR)               |     |

|    | 6.2.2 Bypass Register (BYP)                              |     |

|    | 6.2.3 Boundary Scan Register (BSR)                       |     |

|    | 6.3 TEST ACCESS PORT (TAP) CONTROLLER                    |     |

| 7  | THERMAL MANAGEMENT                                       | 97  |

|    | 7.1 JUNCTION TEMPERATURE                                 | 97  |

|    | 7.2 EXAMPLE OF JUNCTION TEMPERATURE CALCULATION          | 97  |

|    | 7.3 HEATSINK EVALUATION                                  | 97  |

| 8  | PHYSICAL AND ELECTRICAL SPECIFICATIONS                   | 98  |

|    | 8.1 ABSOLUTE MAXIMUM RATINGS                             | 98  |

|    | 8.2 RECOMMENDED OPERATING CONDITIONS                     | 99  |

|    | 8.3 DEVICE POWER CONSUMPTION AND DISSIPATION (TYPICAL) 1 | 100 |

|    | 8.4 DEVICE POWER CONSUMPTION AND DISSIPATION (MAXIMUM) 1 | 101 |

|    | 8.5 D.C. CHARACTERISTICS                                 |     |

|    | 8.6 E1 RECEIVER ELECTRICAL CHARACTERISTICS               |     |

|    | 8.7 T1/J1 RECEIVER ELECTRICAL CHARACTERISTICS            |     |

|    | 8.8 E1 TRANSMITTER ELECTRICAL CHARACTERISTICS            |     |

|    | 8.9 T1/J1 TRANSMITTER ELECTRICAL CHARACTERISTICS         |     |

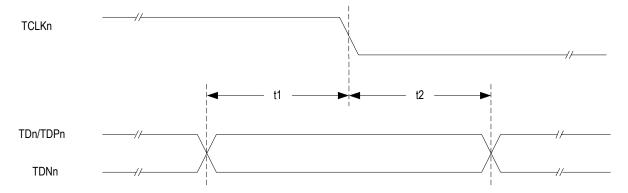

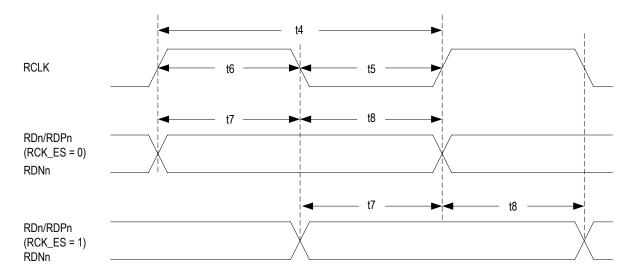

|    | 8.10 TRANSMITTER AND RECEIVER TIMING CHARACTERISTICS     |     |

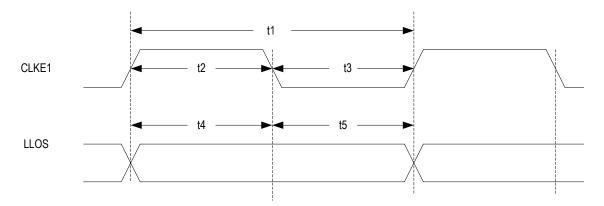

|    | 8.11 CLKE1 TIMING CHARACTERISTICS                        |     |

|    | 8.12 JITTER ATTENUATION CHARACTERISTICS                  |     |

|    | 8.13 MICROPROCESSOR INTERFACE TIMING                     |     |

|    | 8.13.1 Serial Microprocessor Interface                   |     |

|    | 8.14 JTAG TIMING CHARACTERISTICS                         |     |

|    | CLOSSARY                                                 |     |

|    | NDEX                                                     |     |

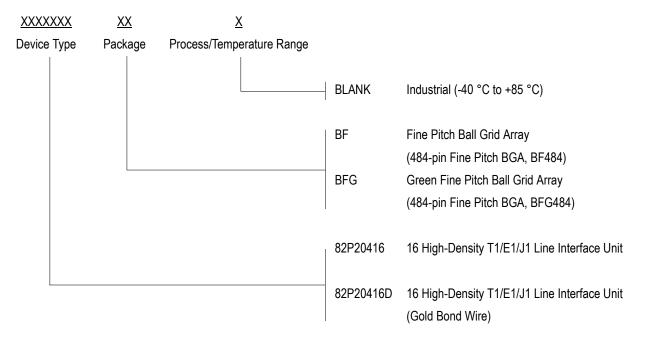

| 01 | PRDERING INFORMATION                                     | 121 |

## **List of Tables**

| Table-1  | Operation Mode Selection                               | 20 |

|----------|--------------------------------------------------------|----|

| Table-2  | Impedance Matching Value in Receive Differential Mode  |    |

| Table-3  | Multiplex Pin Used in Receive System Interface         | 23 |

| Table-4  | Multiplex Pin Used in Transmit System Interface        | 25 |

| Table-5  | PULS[3:0] Setting in T1/J1 Mode                        | 26 |

| Table-6  | PULS[3:0] Setting in E1 Mode                           | 26 |

| Table-7  | Transmit Waveform Value for T1 0 ~ 133 ft              | 28 |

| Table-8  | Transmit Waveform Value for T1 133 ~ 266 ft            | 28 |

| Table-9  | Transmit Waveform Value for T1 266 ~ 399 ft            |    |

| Table-10 | Transmit Waveform Value for T1 399 ~ 533 ft            | 28 |

| Table-11 | Transmit Waveform Value for T1 533 ~ 655 ft            | 28 |

|          | Transmit Waveform Value for E1 75 ohm                  |    |

| Table-13 | Transmit Waveform Value for E1 120 ohm                 | 28 |

| Table-14 | Transmit Waveform Value for J1 0 ~ 655 ft              | 28 |

| Table-15 | Impedance Matching Value in Transmit Differential Mode | 29 |

| Table-16 | EXZ Definition                                         | 33 |

| Table-17 | LLOS Criteria                                          | 34 |

| Table-18 | SLOS Criteria                                          | 35 |

| Table-19 | TLOS Detection Between Two Channels                    | 36 |

| Table-20 | AIS Criteria                                           | 37 |

| Table-21 | Clock Output on CLKT1                                  | 47 |

| Table-22 | Clock Output on CLKE1                                  | 47 |

| Table-23 | Interrupt Summary                                      | 49 |

| Table-24 | After Reset Effect Summary                             | 51 |

# **List of Figures**

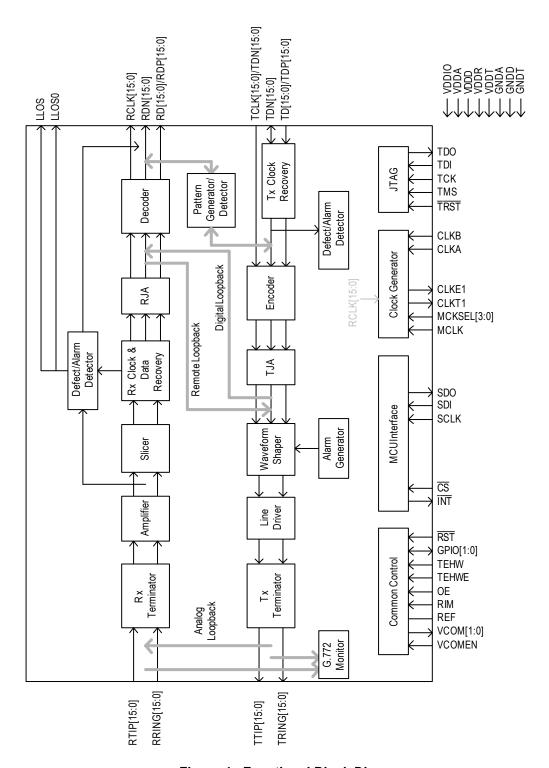

| Figure-1  | Functional Block Diagram                                                                                | 10  |

|-----------|---------------------------------------------------------------------------------------------------------|-----|

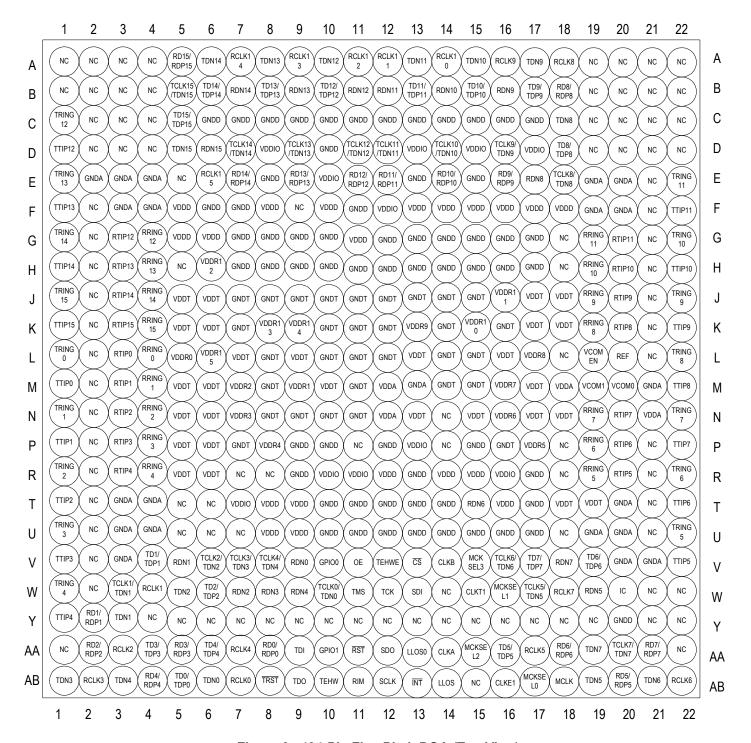

|           | 484-Pin Fine Pitch BGA (Top View)                                                                       |     |

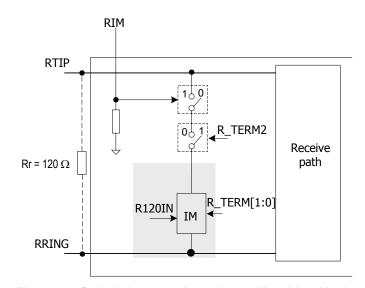

|           | Switch between Impedance Matching Modes                                                                 |     |

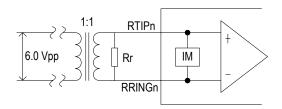

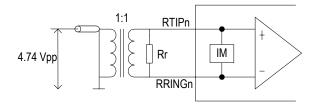

|           | Receive Differential Line Interface with Twisted Pair Cable (with transformer)                          |     |

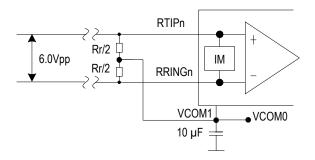

| Figure-5  | Receive Differential Line Interface with Coaxial Cable (with transformer)                               | 21  |

| Figure-6  | Receive Differential Line Interface with Twisted Pair Cable (transformer-less, non standard compliant)  | 22  |

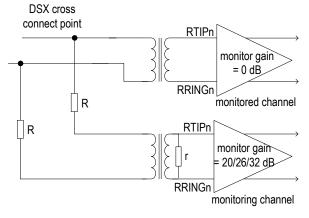

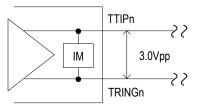

| Figure-7  | Receive Path Monitoring                                                                                 | 22  |

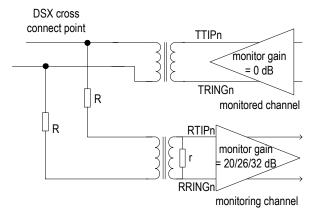

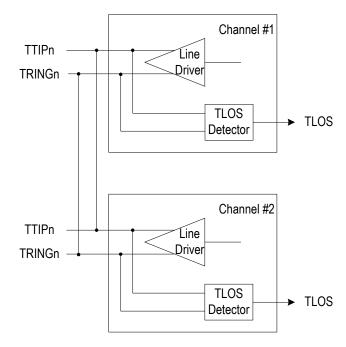

| Figure-8  | Transmit Path Monitoring                                                                                | 22  |

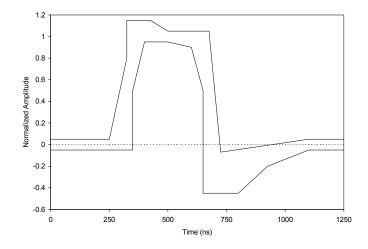

|           | DSX-1 Waveform Template                                                                                 |     |

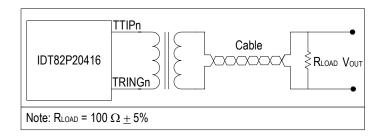

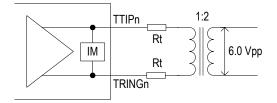

| Figure-10 | T1 Waveform Template Measurement Circuit                                                                | 25  |

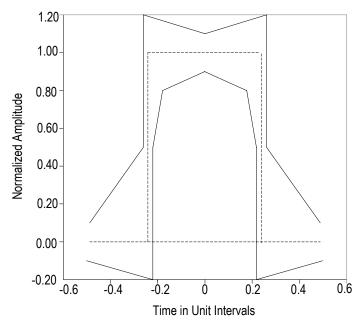

|           | E1 Waveform Template                                                                                    |     |

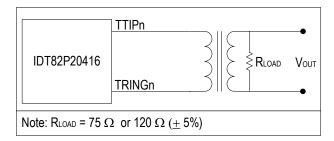

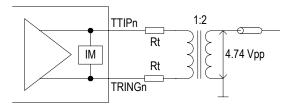

|           | E1 Waveform Template Measurement Circuit                                                                |     |

|           | Transmit Differential Line Interface with Twisted Pair Cable (with Transformer)                         |     |

|           | Transmit Differential Line Interface with Coaxial Cable (with transformer)                              |     |

|           | Transmit Differential Line Interface with Twisted Pair Cable (transformer-less, non standard compliant) |     |

|           | Jitter Attenuator                                                                                       |     |

| •         | LLOS Indication on Pins                                                                                 |     |

| •         | TLOS Detection Between Two Channels                                                                     |     |

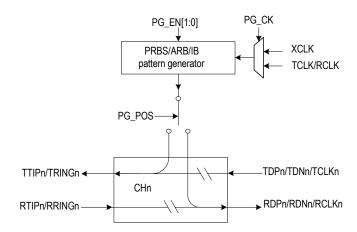

|           | Pattern Generation (1)                                                                                  |     |

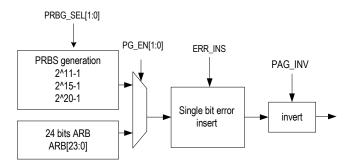

|           | Pattern Generation (2)                                                                                  |     |

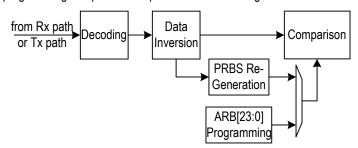

| •         | PRBS / ARB Detection                                                                                    |     |

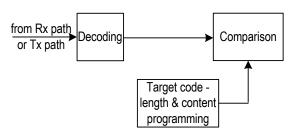

|           | IB Detection                                                                                            |     |

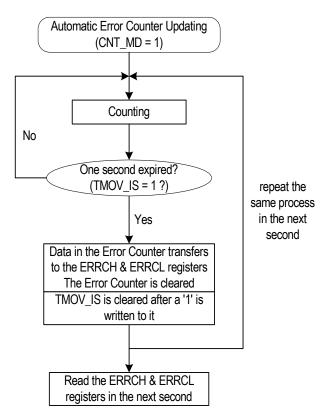

| •         | Automatic Error Counter Updating                                                                        |     |

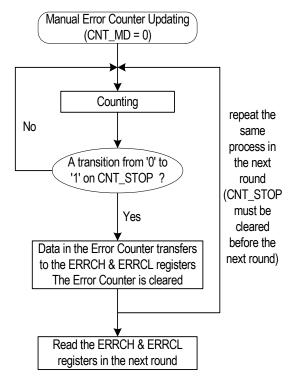

| •         | Manual Error Counter Updating                                                                           |     |

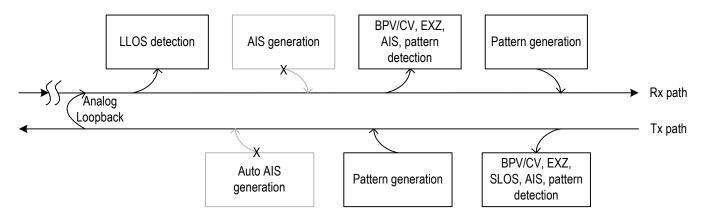

| •         | Priority Of Diagnostic Facilities During Analog Loopback                                                |     |

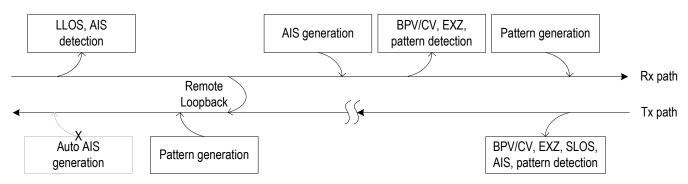

|           | Priority Of Diagnostic Facilities During Manual Remote Loopback                                         |     |

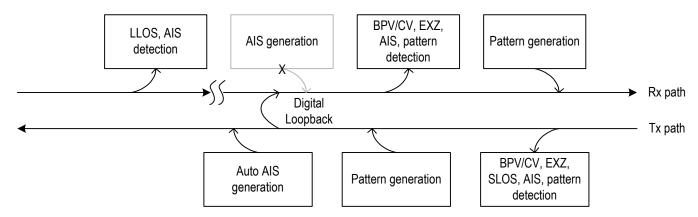

| •         | Priority Of Diagnostic Facilities During Digital Loopback                                               |     |

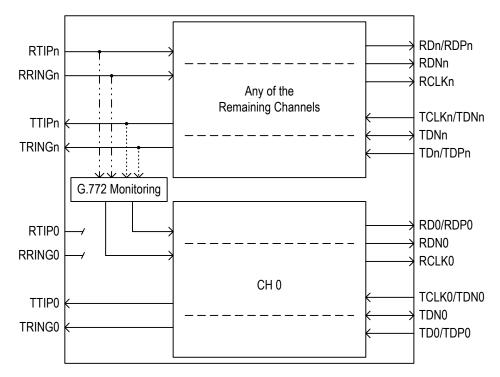

|           | G.772 Monitoring                                                                                        |     |

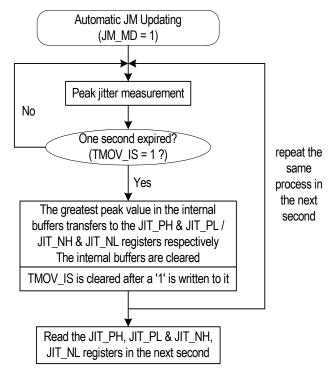

| •         | Automatic JM Updating                                                                                   |     |

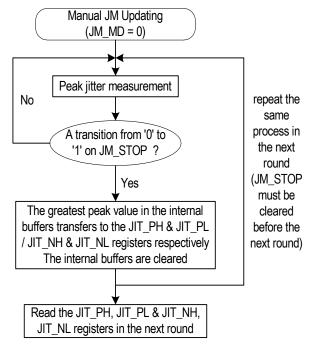

| •         | Manual JM Updating                                                                                      |     |

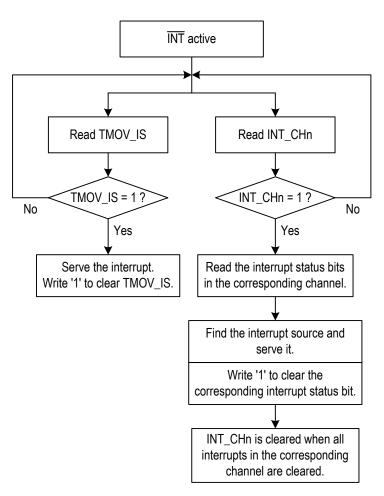

| •         | Interrupt Service Process                                                                               |     |

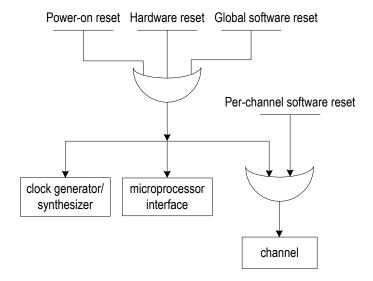

| •         | Reset                                                                                                   |     |

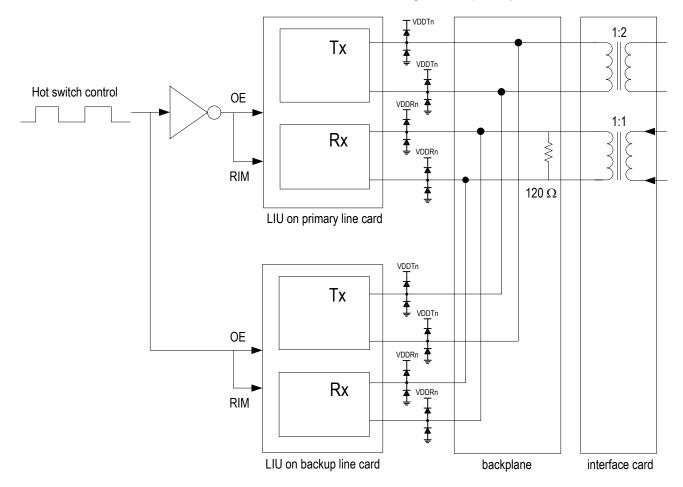

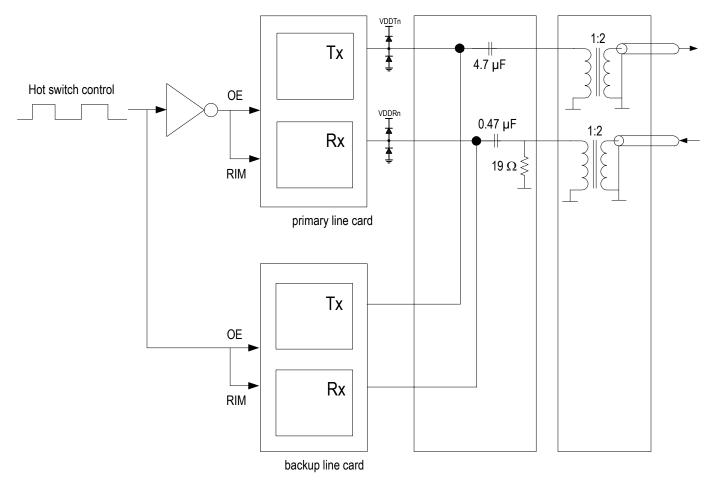

|           | 1:1 HPS Scheme, Differential Interface (Individual Transformer)                                         |     |

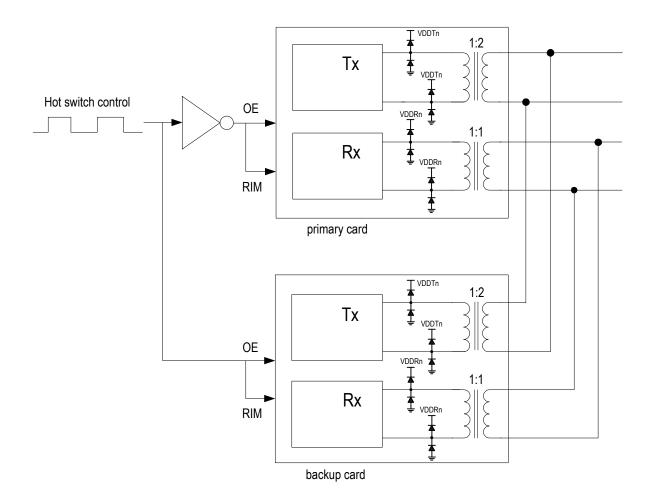

|           | 1+1 HPS Scheme, E1 75 ohm Single-Ended Interface (Shared Common Transformer)                            |     |

| •         | JTAG Architecture                                                                                       |     |

| •         | JTAG State Diagram                                                                                      |     |

| •         | Transmit Clock Timing Diagram                                                                           |     |

| •         | Receive Clock Timing Diagram                                                                            |     |

| •         | CLKE1 Clock Timing Diagram                                                                              |     |

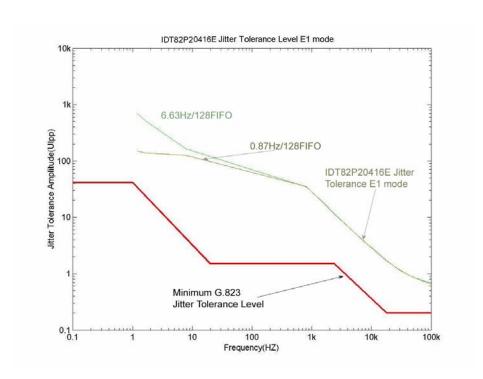

| •         | E1 Jitter Tolerance Performance                                                                         |     |

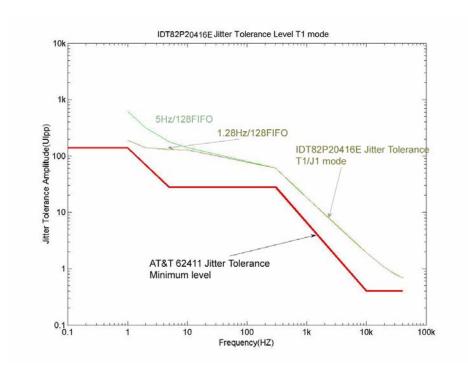

| •         | T1/J1 Jitter Tolerance Performance                                                                      |     |

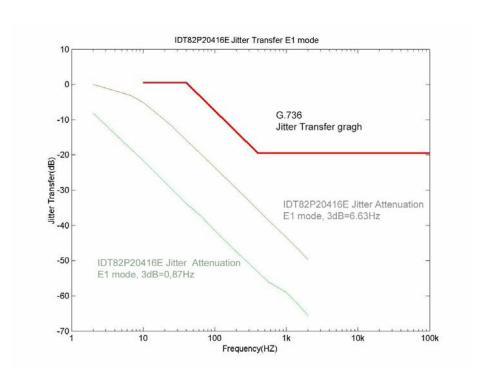

| •         | E1 Jitter Transfer Performance                                                                          |     |

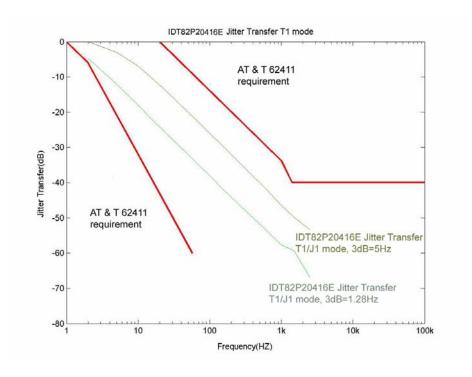

| •         | T1/J1 Jitter Transfer Performance                                                                       |     |

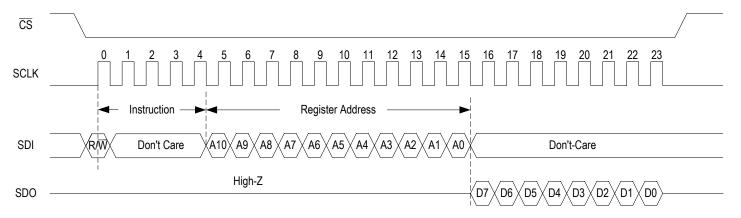

| •         | Read Operation in Serial Microprocessor Interface                                                       |     |

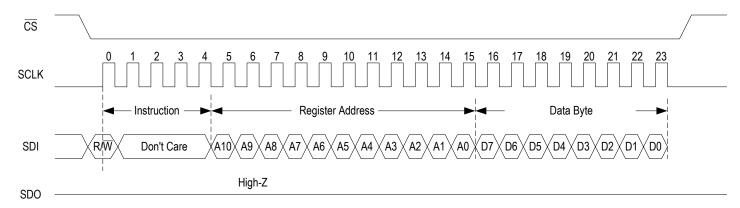

| •         | Write Operation in Serial Microprocessor Interface                                                      |     |

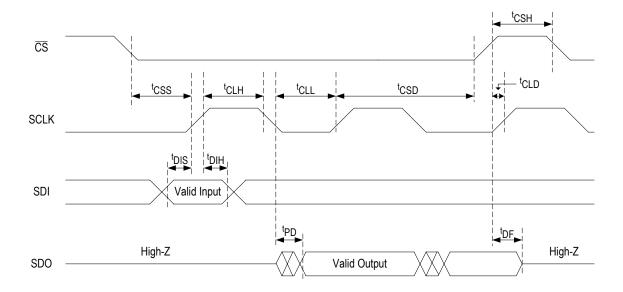

| •         | Timing Diagram                                                                                          |     |

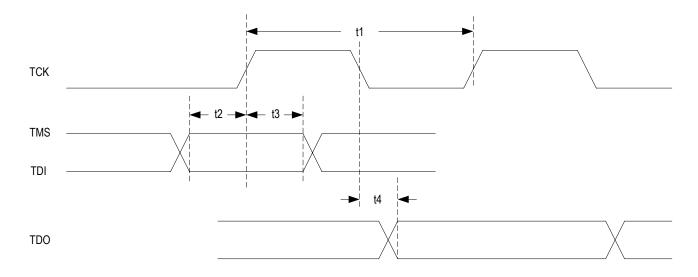

| •         | JTAG Timing                                                                                             | 116 |

# 16-Channel Short Haul T1/E1/J1 Line Interface Unit

IDT82P20416

#### **FEATURES**

- Integrates 16 channels T1/E1/J1 short haul line interface units for 100  $\Omega$  T1, 120  $\Omega$  E1, 110  $\Omega$  J1 twisted pair cable and 75  $\Omega$  E1 coaxial cable applications

- Per-channel configurable Line Interface options

- Fully integrated and software selectable receive and transmit termination

- Option 1: Fully Internal Impedance Matching with integrated receive termination resistor

- Option 2: Partially Internal Impedance Matching with common external resistor for improved device power dissipation

- Option 3: External impedance Matching termination

- Supports global configuration and per-channel configuration to T1, E1 or J1 mode

#### ◆ Per-channel programmable features

- Provides T1/E1/J1 short haul waveform templates and userprogrammable arbitrary waveform templates

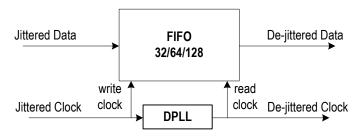

- Provides two JAs (Jitter Attenuator) for each channel of receiver and transmitter

- Supports AMI/B8ZS (for T1/J1) and AMI/HDB3 (for E1) encoding and decoding

#### ◆ Per-channel System Interface options

- Supports Single Rail, Dual Rail with clock or without clock and sliced system interface

- Integrated Clock Recovery for the transmit interface to recover transmit clock from system transmit data

#### Per-channel system and diagnostic functions

- Provides transmit driver over-current detection and protection with optional automatic high impedance of transmit interface

- Detects and generates PRBS (Pseudo Random Bit Sequence), ARB (Arbitrary Pattern) and IB (Inband Loopback) in either receive or transmit direction

- Provides defect and alarm detection in both receive and transmit directions.

- Defects include BPV (Bipolar Violation) /CV (Code Violation) and EXZ (Excessive Zeroes)

- Alarms include LLOS (Line LOS), SLOS (System LOS), TLOS (Transmit LOS) and AIS (Alarm Indication Signal)

- Programmable LLOS detection /clear levels. Compliant with ITU and ANSI specifications

- · Various pattern, defect and alarm reporting options

- Serial hardware LLOS reporting (LLOS, LLOS0) for all 16 channels

- Register access to individual registers or 16-bit error counters

- Supports Analog Loopback, Digital Loopback and Remote Loopback

- Supports T1.102 line monitor

#### ◆ Hitless Protection Switching (HPS) without external Relays

- Supports 1+1 and 1:1 hitless protection switching

- Asynchronous hardware control (OE, RIM) for fast global high impedance of receiver and transmitter (hot switching between working and backup board)

- · High impedance transmitter and receiver while powered down

- Per-channel register control for high impedance, independent for receiver and transmitter

#### Clock Inputs and Outputs

- Flexible master clock (N x 1.544 MHz or N x 2.048 MHz) (1  $\leq$  N  $\leq$  8, N is an integer number)

- Integrated clock synthesizer can multiply or divide the reference clock to a wide range of frequencies: 8 KHz, 64 KHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 19.44 MHz and 32.768 MHz

#### ♦ Microprocessor Interface

· Supports Serial microprocessor interface

#### **♦** Other Key Features

- · IEEE1149.1 JTAG boundary scan

- Two general purpose I/O pins

- 3.3 V I/O with 5 V tolerant inputs

- 3.3 V and 1.8 V power supply

- · Package: 484-pin Fine Pitch BGA (19 mm X 19 mm)

#### Applicable Standards

- AT&T Pub 62411 Accunet T1.5 Service

- ANSI T1.102, T1.403 and T1.231

- Bellcore TR-TSY-000009, GR-253-CORE and GR-499-CORE

- ETSI CTR12/13

- ETS 300166 and ETS 300 233

- G.703, G.735, G.736, G.742, G.772, G.775, G.783 and G.823

- 0.161

- ITU I.431 and ITU O.171

#### **APPLICATIONS**

- ◆ SDH/SONET multiplexers

- ◆ Central office or PBX (Private Branch Exchange)

- ◆ Digital access cross connects

- ◆ Remote wireless modules

- ◆ Microwave transmission systems

#### **DESCRIPTION**

The IDT82P20416 is a 16-channel high-density T1/E1/J1 short haul Line Interface Unit. Each channel of the IDT82P20416 can be independently configured. The configuration is performed through a Serial microprocessor interface.

In the receive path, through a Single Ended or Differential line interface, the received signal is processed by an adaptive Equalizer and then sent to a Slicer. Clock and data are recovered from the digital pulses output from the Slicer. After passing through an enabled or disabled Receive Jitter Attenuator, the recovered data is decoded using B8ZS/AMI/HDB3 line code rule in Single Rail NRZ Format mode and output to the system, or output to the system without decoding in Dual Rail NRZ Format mode and Dual Rail RZ Format mode.

In the transmit path, the data to be transmitted is input on TDn in Single Rail NRZ Format mode or TDPn/TDNn in Dual Rail NRZ Format mode and Dual Rail RZ Format mode, and is sampled by a transmit reference clock. The clock can be supplied externally from TCLKn or recovered from the input transmit data by an internal Clock Recovery. A selectable JA in Tx path is used to de-jitter gapped clocks. To meet T1/E1/J1 waveform standards, five preset T1 templates, two E1 templates and one J1 template, as well as an arbitrary waveform generator are provided. The data through the Waveform Shaper, the Line Driver and the Tx Transmitter is output on TTIPn and TRINGn.

Alarms (including LOS, AIS) and defects (including BPV, EXZ) are detected in both receive line side and transmit system side. AIS alarm, PRBS, ARB and IB patterns can be generated /detected in receive / transmit direction for testing purpose. Analog Loopback, Digital Loopback and Remote Loopback are all integrated for diagnostics.

A line monitor function per T1.102 is available to provide a Non-Intrusive Monitoring of channels of other devices.

JTAG per IEEE 1149.1 is also supported by the IDT82P20416.

Applications 9 December 17, 2009

#### **BLOCK DIAGRAM**

Figure-1 Functional Block Diagram

Block Diagram 10 December 17, 2009

#### 1 PIN ASSIGNMENT

Figure-2 484-Pin Fine Pitch BGA (Top View)

Pin Assignment 11 December 17, 2009

#### **2 PIN DESCRIPTION**

| Name     | 1/0            | Pin No. <sup>1</sup>                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------|----------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | Line Interface |                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| RTIPn    |                |                                                                          | RTIPn / RRINGn: Receive Bipolar Tip/Ring for Channel 0 ~ 15 The receive line interface supports both Receive Differential mode and Receive Single Ended                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RRINGn   |                | L4, M4, N4, P4, R4, R19, P19, N19,                                       | mode.  In Receive Differential mode, the received signal is coupled into RTIPn and RRINGn via a 1:1                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| (n=0~15) |                | K19, J19, H19, G19, G4, H4, J4, K4                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|          |                |                                                                          | <ul> <li>During and after power-on reset, hardware reset or global software reset;</li> <li>Per-channel High-Z</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|          |                |                                                                          | - Receiver power down by writing '1' to the R_OFF bit (b5, RCF0,)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| TTIPn    | Output         |                                                                          | TTIPn / TRINGn: Transmit Bipolar Tip /Ring for Channel 0 ~ 15 The transmit line interface supports both Transmit Differential mode and Transmit Single                                                                                                                                                                                                                                                                                                                                                          |  |  |

| TRINGn   |                |                                                                          | Ended mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| (n=0~15) |                | L1, N1, R1, U1, W1, U22, R22, N22,<br>L22, J22, G22, E22, C1, E1, G1, J1 | puts a negative differential pulse. The pulses are coupled to the line side via a 1:2 (step up) transformer or without a transformer (transformer-less).  In Transmit Single Ended mode, TRINGn should be left open (it is shorted to ground internally). The signal presented at TTIPn is output to the line side via a 1:2 (step up) transformer. These pins will become High-Z globally or channel specific in the following conditions:  • Global High-Z:  - Connecting the OE pin to low;  - Loss of MCLK; |  |  |

|          |                |                                                                          | <ul> <li>During and after power-on reset, hardware reset or global software reset;</li> <li>Per-channel High-Z</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|          |                |                                                                          | <ul> <li>Writing '0' to the OE bit (b6, TCF0,) <sup>2</sup>;</li> <li>Loss of TCLKn in Transmit Single Rail NRZ Format mode or Transmit Dual Rail NRZ Format mode, except that the channel is in Remote Loopback or transmit internal pattern with XCLK <sup>3</sup>;</li> </ul>                                                                                                                                                                                                                                |  |  |

|          |                |                                                                          | <ul> <li>Transmitter power down by writing '1' to the T_OFF bit (b5, TCF0,);</li> <li>Per-channel software reset;</li> <li>The THZ_OC bit (b4, TCF0,) is set to '1' and the transmit driver over-current is</li> </ul>                                                                                                                                                                                                                                                                                          |  |  |

|          |                |                                                                          | detected. Refer to Section 3.3.8 Output High-Z on TTIP and TRING for details.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

#### Note:

- 1. The pin number of the pins with the footnote 'n' is listed in order of channel (CH0  $\sim$  CH15).

- 2. The content in the brackets indicates the position and the register name of the preceding bit. After the register name, if the punctuation ',...' is followed, this bit is in a per-channel register. The addresses and details are included in Chapter 5 Programming Information.

- 3. XCLK is derived from MCLK. It is 1.544 MHz in T1/J1 mode or 2.048 MHz in E1 mode.

Pin Description 12 December 17, 2009

| Name                   | 1/0                                                   | Pin No.                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                       |                                                                                    | System Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RDn / RDPn<br>(n=0~15) | 0~15) AA18, AA21, B18, E16, E14, E12, E11, E9, E7, A5 |                                                                                    | RDn: Receive Data for Channel 0 ~ 15 When the receive system interface is configured to Single Rail NRZ Format mode, this multiplex pin is used as RDn. The decoded NRZ data is updated on the active edge of RCLKn. The active level on RDn is selected by the RD_INV bit (b3, RCF1,). When the receiver is powered down, RDn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        |                                                       |                                                                                    | RDPn: Positive Receive Data for Channel 0 ~ 15  When the receive system interface is configured to Dual Rail NRZ Format mode, Dual Rail RZ Format mode or Dual Rail Sliced mode, this multiplex pin is used as RDPn.  In Receive Dual Rail NRZ Format mode, the un-decoded NRZ data is output on RDPn and RDNn and updated on the active edge of RCLKn.  In Receive Dual Rail RZ Format mode, the un-decoded RZ data is output on RDPn and RDNn and updated on the active edge of RCLKn.  In Receive Dual Rail Sliced mode, the raw RZ sliced data is output on RDPn and RDNn.  For Receive Differential line interface, an active level on RDPn indicates the receipt of a positive pulse on RTIPn and a negative pulse on RRINGn; while an active level on RDNn indicates the receipt of a negative pulse on RTIPn and a positive pulse on RRINGn.  For Receive Single Ended line interface, an active level on RDPn indicates the receipt of a positive pulse on RTIPn; while an active level on RDNn indicates the receipt of a negative pulse on RTIPn.  The active level on RDPn and RDNn is selected by the RD_INV bit (b3, RCF1,).  When the receiver is powered down, RDPn and RDNn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,). |

| RDNn<br>(n=0~15)       | Output                                                | V9, V5, W7, W8, W9, W19, T15,<br>V18, E17, B16, B14, B12, B11, B9,<br>B7, D6       | RDNn: Negative Receive Data for Channel 0 ~ 15 When the receive system interface is configured to Dual Rail NRZ Format mode, Dual Rail RZ Format mode or Dual Rail Sliced mode, this multiplex pin is used as RDNn. (Refer to the description of RDPn for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RCLKn<br>(n=0~15)      | Output                                                | AB7, W4, AA3, AB2, AA7, AA17,<br>AB22, W18, A18, A16, A14, A12,<br>A11, A9, A7, E6 | RCLKn: Receive Clock for Channel 0 ~ 15  When the receive system interface is configured to Single Rail NRZ Format mode, Dual Rail NRZ Format mode or Dual Rail RZ Format mode, this multiplex pin is used as RCLKn. RCLKn outputs a 1.544 MHz (in T1/J1 mode) or 2.048 MHz (in E1 mode) clock which is recovered from the received signal.  The data output on RDPn/RDNn (in Receive Dual Rail NRZ Format mode, Receive Dual Rail RZ Format mode and Receive Dual Rail Sliced) is updated on the active edge of RCLKn. The active edge is selected by the RCK_ES bit (b4, RCF1,).  In LLOS condition, RCLKn output high or XCLK, as selected by the RCKH bit (b7, RCF0,) (refer to Section 3.5.3.1 Line LOS (LLOS) for details).  When the receiver is powered down, RCLKn will be in High-Z state or low, as selected by the RHZ bit (b6, RCF0,).                                                                                                                                                                                                                                                                                                                                                                                                                  |

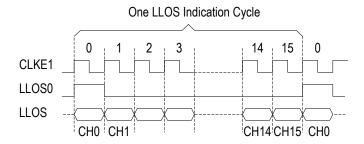

| LLOS                   | Output                                                | AB14                                                                               | LLOS: Receive Line Loss Of Signal  LLOS synchronizes with the output of CLKE1 and can indicate the LLOS (Line LOS) status of all 16 channels in a serial format.  When the clock output on CLKE1 is enabled, LLOS indicates the LLOS status of the 16 channels in a serial format and repeats every seventeen cycles. The start filler is positioned by LLOS0. Refer to the description of LLOS0 below for details.  LLOS is updated on the rising edge of CLKE1 and is always active high.  When the clock output of CLKE1 is disabled, LLOS will be held in High-Z state.  (Refer to Section 3.5.3.1 Line LOS (LLOS) for details.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Pin Description 13 December 17, 2009

| Name                     | 1/0            | Pin No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                | Description                                                                                                                                                                                                           |                                  |

|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LLOS0                    | Output         | AA13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LLOS0: Receive Line Loss Of Signal for Start Position LLOS0 can indicate the start position on the LLOS pin. When the clock output on CLKE1 is enabled, LLOS0 pulses high for one CLKE1 clock cycle to indicate the start position on the LLOS pin. When CLKE1 outputs 8 KHz clock, LLOS0 pulses high for one 8 KHz clock cycle (125 μs) every seventeen 8 KHz clock cycles; when CLKE1 outputs 2.048 MHz clock, LLOS0 pulses high for one 2.048 MHz clock cycle (488 ns) every seventeen 2.048 MHz clock cycles. LLOS0 is updated on the rising edge of CLKE1. When the clock output on CLKE1 is disabled, LLOS0 will be held in High-Z state. (Refer to Section 3.5.3.1 Line LOS (LLOS) for details.) |                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |                                  |

| TDn / TDPn<br>(n=0~15)   | Input          | AB5, V4, W6, AA4, AA6, AA16, V19, V17, D18, B17, B15, B13, B10, B8, B16, C5  TDn: Transmit Data for Channel 0 ~ 15  When the transmit system interface is configured to 3 plex pin is used as TDn.  TDn accepts Single Rail NRZ data. The data is samp TCLKn.  The active level on TDn is selected by the TD_INV bit TDPn: Positive Transmit Data for Channel 0 ~ 15  When the transmit system interface is configured to 1 RZ Format mode, this multiplex pin is used as TDPn.  In Transmit Dual Rail NRZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, the pre-encorate in Transmit Dual Rail RZ Format mode, th |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | the is configured to Single R  a. The data is sampled into d by the TD_INV bit (b3, TO  or Channel 0 ~ 15 the is configured to Dual Rain is used as TDPn. at mode, the pre-encoded edge of TCLKn.  node, the pre-encoded RZ of | sampled into the device on the active edge of INV bit (b3, TCF1,).  ~ 15 ed to Dual Rail NRZ Format mode or Dual Rail IDPn. pre-encoded NRZ data is input on TDPn and fin. encoded RZ data is input on TDPn and TDNn. |                                  |

|                          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TDPn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TDNn                                                                                                                                                                                                                           | Output Pulse on TTIPn                                                                                                                                                                                                 | Output Pulse on TRINGn *         |

|                          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                              | Space                                                                                                                                                                                                                 | Space                            |

|                          |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                              | Negative Pulse                                                                                                                                                                                                        | Positive Pulse                   |